您现在的位置是:主页 > 基础 > 其他基础电路图 >

74ls373中文资料_74ls373功能引脚图及应用电路图-其他基础电路图

发布时间:2022-09-12 17:28:04所属栏目:其他基础电路图 已帮助人编辑作者:电路图知识网

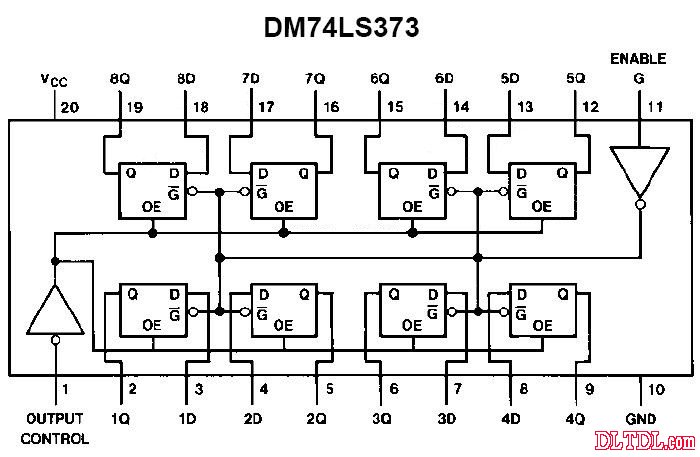

54LS373 /74373 三态缓冲输出的8D锁存器(3S,锁存允许输入有回环特性)

54LS373/74LS373 17ns 120mW

54LS373/74LS373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端 LE 为高电平时,O 随数据 D 而变。当 LE 为低电平时,O 被锁存在已建立的数据电平。

当 LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善 400mV。

图1引脚功能图

管脚引出端功能符号

D0~D7 数据输入端

OE 三态允许控制端(低电平有效)

LE 锁存允许端

O0~O7 输出端

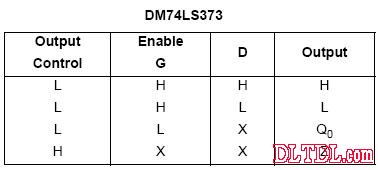

真值表:

L--低电平;

H--高电平;

X--不定态;

Q0--建立稳态前Q的电平;

G--输入端,与8031ALE连高电平:畅通无阻低电平:关门锁存。图中OE--使能端,接地。

当G=“1”时,74LS373输出端1Q-8Q与输入端1D-8D相同;

当G为下降沿时,将输入数据锁存。

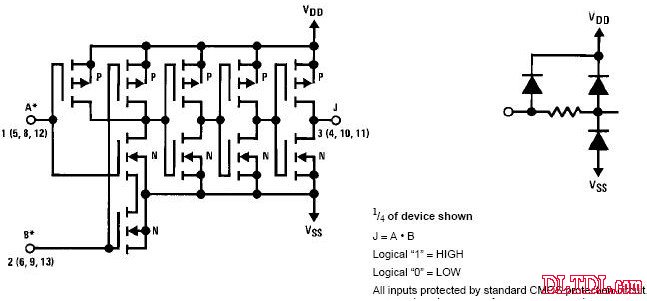

图2 54LS373/74LS373内部逻辑电路图

Tags:

相关文章

猜你喜欢

可控硅与场效应管及三极管的区别-其他基础电路图

可控硅与场效应管及三极管的区别 1.场效应管的源极s、栅极g、漏极d分别对应...

CD4071 CD4081中文资料_CD4071功能引脚图_CD4081应用电路图-其他基础电路图

CD4071 四2输入端或门OR NSC/TI CD4081 四2输入端与门AND NSC/HIT/TI CD4071真值表:Y=A+B...

采用RS触发器的防抖电路-其他基础电路图

所示为采用RS触发器的防抖动电路。由图可 知,在开关的触点部位加了RC积分电...

由T触发器组成的非同步即使输球电路及其信号波形-其他基础电路图

所示是利用T触发器组成的计数器电路及其信号波形,它是一种非同步式计数器...

其他基础电路图相关资讯

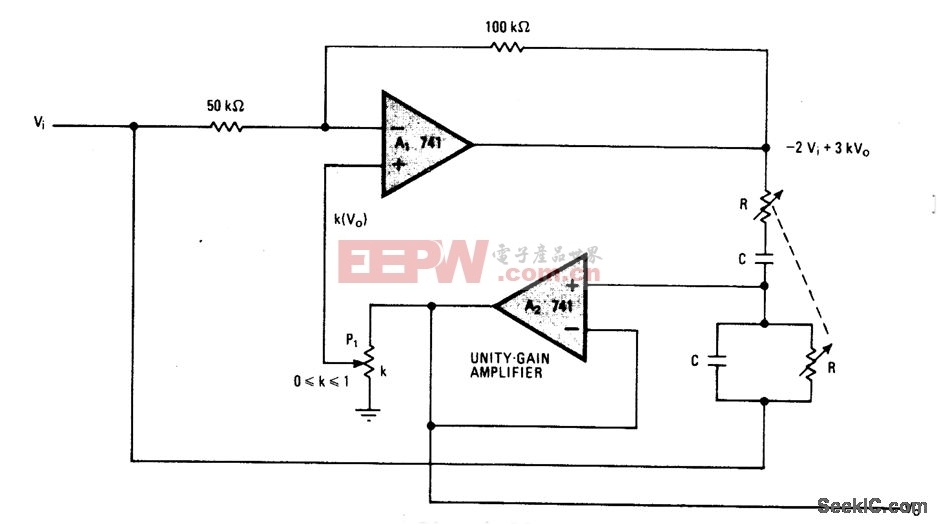

稳压用运算放大器基本电-其他基础电路图

可选择带宽的NOTCH滤波器-其他基础电路图

多路脉冲编码器-其他基础电路图

焊锡技术-教你怎样使焊锡点光亮-其他基础电路图

采用CMOS或非门的防抖动电路-其他基础电路图

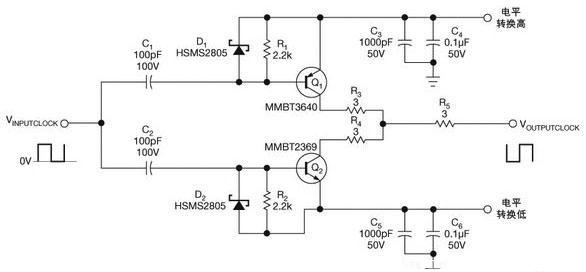

简易电平转换电路图-其他基础电路图

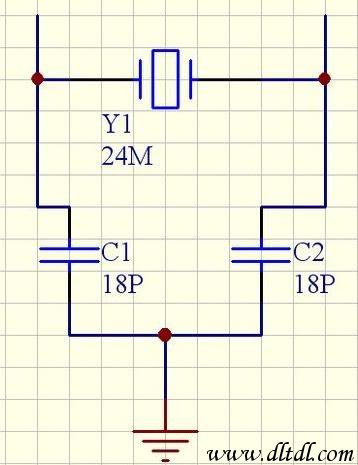

晶振负载电容的计算-其他基础电路图

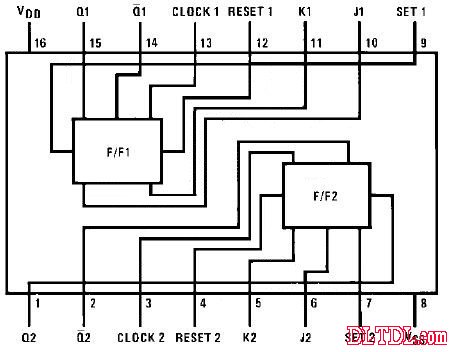

CD4027中文资料-其他基础电路图

供电耦合器一晶闸管的接口电路a-其他基础电路图

经典实用的单片机模块电路设计_单片机电路图-其他基础电路图

具有75欧同辅导线的阻抗-其他基础电路图

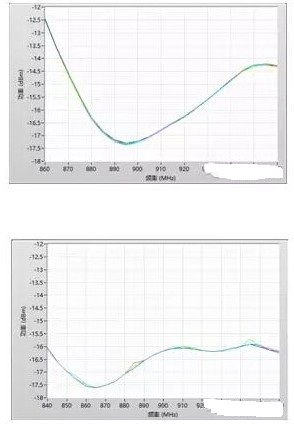

超高频射频识别标签灵敏度的测试方法及解决方案-其他基础电路图

电阻器好坏的判断与检测-其他基础电路图

LM7824A中文资料-其他基础电路图

提高功率因数的方法-其他基础电路图