您现在的位置是:主页 > 基础 > 其他基础电路图 >

时序一致性测试解决方案-其他基础电路图

发布时间:2023-03-24 02:05:13所属栏目:其他基础电路图 已帮助人编辑作者:电路图知识网

在某产品测试过程中,工程师反馈偶尔会出现数据异常,经过系统性的分析,致远电子测试团队推测可能是ADC芯片的SPI通信总线的时序存在偶发异常,但由于异常出现概率很低,该如何对SPI通信总线偶发的时序问题进行定位呢?

一、搭建测试环境

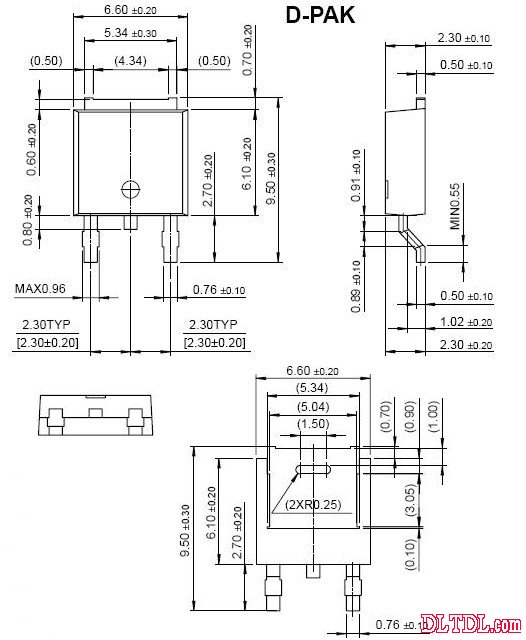

SPI总线测试点位于主机的主板底部,时钟频率大约为33MHz,属高频信号,所以对探头的端接方式比较讲究;为了方便测试,如图1所示,用短线将测试点引出,探头的地线也从前端自绕线引出,这样可以提高信号完整性,减少示波器采样对时序分析过程的影响。

图1 探头端接测试点

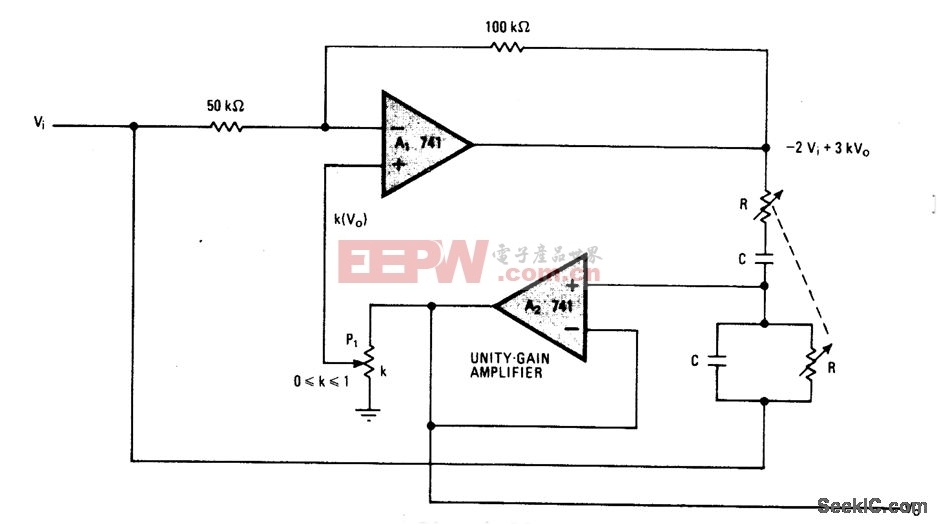

二、长时间监测定位异常

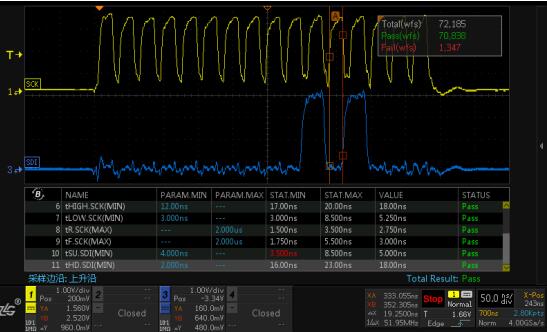

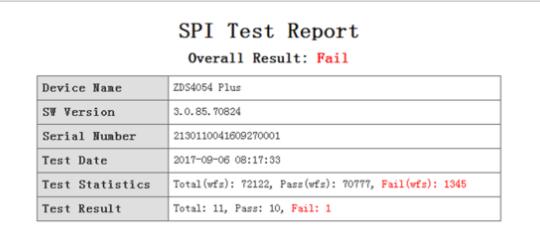

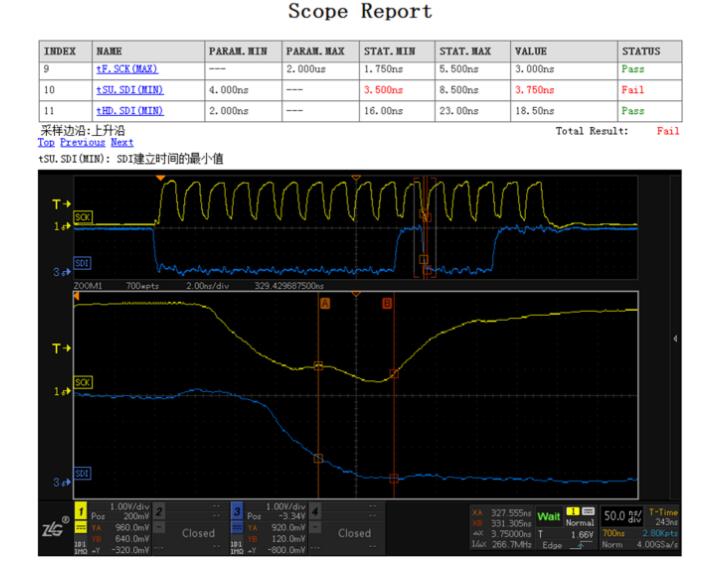

ZDS4000的时序分析软件具备长时间统计功能,下班后设置好示波器,对数据采集仪的SPI总线时序连续监测一个晚上,第二天上班的时候,导出监测分析结果,如图2所示,一个晚上总共进行了72185次测量,其中有1347次是测量失败的,导致异常的原因是SPI的数据建立时间不满足后级芯片的时序要求。示波器自动保存了这1347份失败的测试,打开第1345份测试,如图3所示,显示了当前建立时间为3.75ns(包含时序违规处截图),不满足后级芯片4ns建立时间的要求,而且历史出现差的时序是3.5ns,时序是8.5ns,问题得以定位。

图2 时序分析统计结果

图3 测量结果失败报表

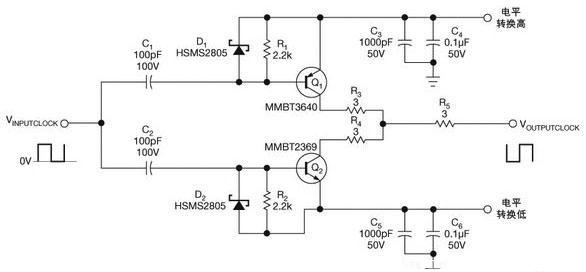

三、定位问题并做稳定性验证

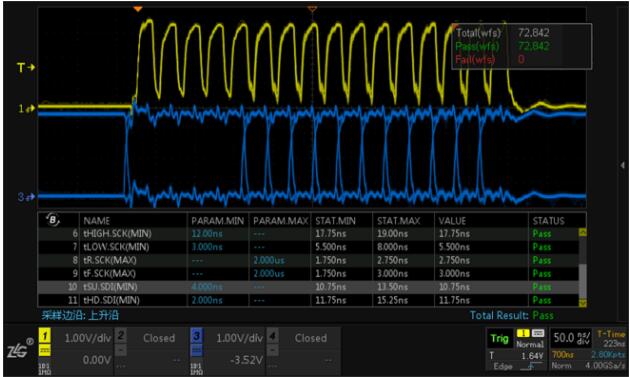

通过上述测试分析,SPI总线的建立时间偏小,保持时间偏大,调整时钟信号时序延迟6.5ns左右,就可得到较好时序分析,即将数据信号建立时间和数据信号保持时间尽可能接近。整改之后再次用时序分析软件对SPI总线进行一夜的稳定性测量,测量结果如图4所示,进行了72842次时序分析,所有测试都通过,且每一项测量项都PASS。之前的问题项建立时间,值10.75ns,值13.5ns,非常完美,这显示了 SPI总线的时序非常稳定性。

图4 时序分析测量结果

时序的一致性和稳定性分析,一直以来都是业界难题。当前ZLG致远电子的时序一致性测试方案已经支持I2C、SPI、I2S和MIPI-RFFE。

Tags:

相关文章

猜你喜欢

可控硅与场效应管及三极管的区别-其他基础电路图

可控硅与场效应管及三极管的区别 1.场效应管的源极s、栅极g、漏极d分别对应...

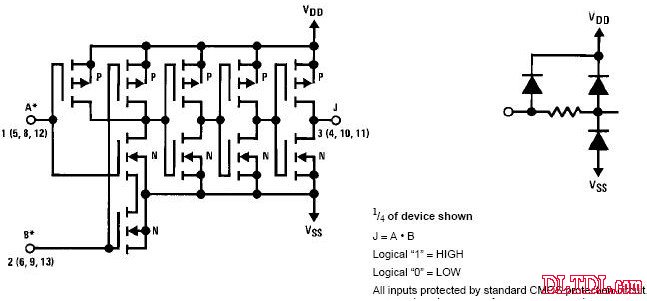

CD4071 CD4081中文资料_CD4071功能引脚图_CD4081应用电路图-其他基础电路图

CD4071 四2输入端或门OR NSC/TI CD4081 四2输入端与门AND NSC/HIT/TI CD4071真值表:Y=A+B...

采用RS触发器的防抖电路-其他基础电路图

所示为采用RS触发器的防抖动电路。由图可 知,在开关的触点部位加了RC积分电...

由T触发器组成的非同步即使输球电路及其信号波形-其他基础电路图

所示是利用T触发器组成的计数器电路及其信号波形,它是一种非同步式计数器...

其他基础电路图相关资讯

多路脉冲编码器-其他基础电路图

提高功率因数的方法-其他基础电路图

稳压用运算放大器基本电-其他基础电路图

焊锡技术-教你怎样使焊锡点光亮-其他基础电路图

晶振负载电容的计算-其他基础电路图

供电耦合器一晶闸管的接口电路a-其他基础电路图

采用CMOS或非门的防抖动电路-其他基础电路图

经典实用的单片机模块电路设计_单片机电路图-其他基础电路图

电阻器好坏的判断与检测-其他基础电路图

LM7824A中文资料-其他基础电路图

具有75欧同辅导线的阻抗-其他基础电路图

可选择带宽的NOTCH滤波器-其他基础电路图

简易电平转换电路图-其他基础电路图

CD4027中文资料-其他基础电路图

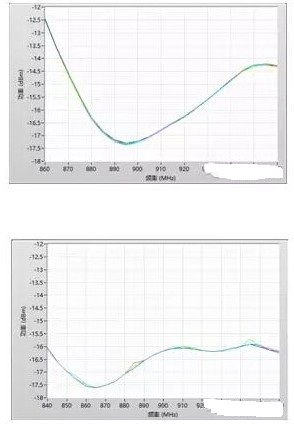

超高频射频识别标签灵敏度的测试方法及解决方案-其他基础电路图