集成电路构成的信号产生电路图

最近更新

-

混合集成电路EMC的设计-集成电路构成的信号产生电路图

本文详细阐述了混合集成电路电磁干扰产生的原因,并结合混合集成电路的工艺特点提出了系统电磁兼容设计中应注意的问题和采取的具体措施,为提高混合集成电路的电磁兼容性奠定了基础。 1引言 混合集成电路(Hybrid Integrated Circuit)是由半导体集成工艺与厚(薄)膜工艺...

2022-09-19【集成电路构成的信号产生电路图】

阅读全文 -

利用ADMS平台加速混合信号集成电路设计-集成电路构成的信号产生电路图

越来越多的设计正向混合信号发展,IBS公司预测显示,到2006年所有集成电路设计中有73%将为混合信号设计。目前混合信号技术成为EDA业内为热门的话题。深亚微米及纳米技术的发展促使芯片设计与制造由单个IC、ASIC向SoC转变,现在SoC也由数字SoC全面转向混合SoC,成为...

2022-10-28【集成电路构成的信号产生电路图】

阅读全文 -

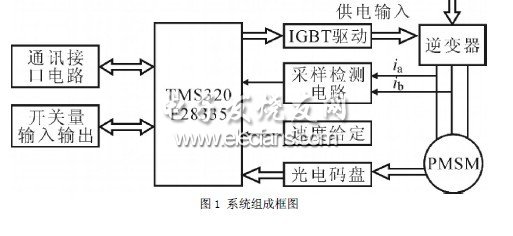

三大电机控制方案之DSP篇:TMS320F28335-集成电路构成的信号产生电路图

近几年来,基于DSP的电机专用集成电路由于在计算速度、容量存储等方面比单片机具有更优的性能,已逐渐代替单片机运用于电机控制系统中。目前的大部分电机都把电流环控制作为DSP的一个协处理来考虑,而速度或位置环控制则由 DSP芯片来实现。一般情况下,由于...

2023-04-28【集成电路构成的信号产生电路图】

阅读全文 -

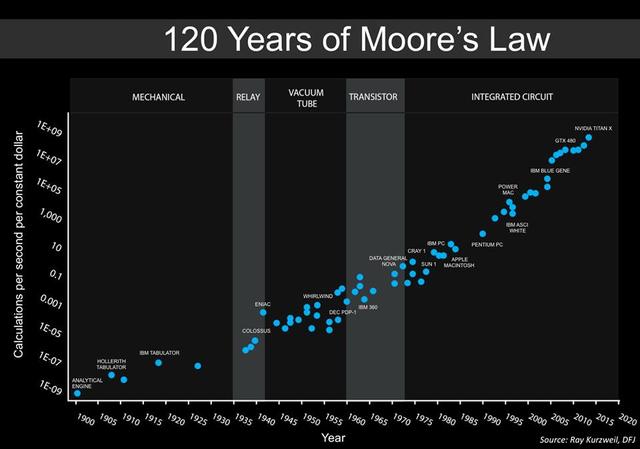

关于摩尔定律知识汇总-集成电路构成的信号产生电路图

已经稳固运行了 50 年之久的摩尔定律就将迎来终结,但这背后也蕴藏着大量的机会。原文来自 Rodney Brooks 的博客。 摩尔定律到底从何而来 Moore, Gordon E., Cramming more components onto integrated circuits, Electronics, Vol 32, No. 8, April 19, 1965. Electronics 是一本 1930 年到 1995 年期间出刊的...

2023-03-17【集成电路构成的信号产生电路图】

阅读全文 -

异步DSP设计:更低功耗,更高性能-集成电路构成的信号产生电路图

目前,处理器性能的主要衡量指标是时钟频率。绝大多数的集成电路 (IC) 设计都基于同步架构,而同步架构都采用一致的时钟。这种架构非常普及,许多人认为它也是数字电路设计的途径。然而,有一种截然不同的设计技术即将走上前台:异步设计。 这一新技术的...

2022-11-26【集成电路构成的信号产生电路图】

阅读全文 -

一种集成电路开短路测试方案详解-集成电路构成的信号产生电路图

集成电路开短路测试分为开路测试(open short to VDD)和短路测试(open short to VSS)。 一般来说,芯片的每个引脚都有泄放或保护电路是两个首尾相连的二极管,一端接VDD,一端接VSS,信号是从两个二极管的接点进来测试时测试时,先把芯片的VDD引脚接0伏(或接地),再...

2023-04-11【集成电路构成的信号产生电路图】

阅读全文 -

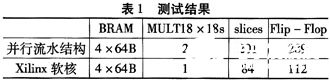

通过并行流水线结构实现直接型FIR滤波器的系统设计方案-集成电路构成的信号

1 、并行流水结构FIR的原理 在用FPGA或专用集成电路实现数字信号处理算法时,计算速度和芯片面积是两个相互制约的主要问题。实际应用FIR滤波器时,要获得良好的滤波效果,滤波器的阶数可能会显著增加,有时可能会多达几百阶。因此,有必要在性能和实现复杂性...

2023-03-27【集成电路构成的信号产生电路图】

阅读全文

- 共 1页7条记录