您现在的位置是:主页 > 信号处理 >

测试环路滤波器及射频电路设计详解-信号处理电子电路图

发布时间:2022-12-16 01:25:55所属栏目:信号处理 已帮助人编辑作者:电路图知识网

小数分频频率合成器在测试时必须外接一个环路滤波器电路与压控振荡器才能构成一个完整的锁相环电路。其外围电路中环路滤波器的设计好坏将直接影响到芯片的性能测试。以ADF4153($2.5200)小数分频频率合成器为例,研究了其外围环路滤波器的设计方法,给出了基于芯片测试的环路滤波器设计流程,并进行了验证测试。测试结果表明,该滤波器可满足小数分频频率合成器芯片测试的需要。在进行小数分频频率合成器的芯片测试时,数字部分可以通过常规的数字测试方法即可以实现;而输出射频信号的相位噪声、杂散噪声则需要芯片工作在正常的输出状态下才能测试。小数分频频率合成器芯片在测试时需要与外接环路滤波器(LF)、压控振荡器(VCO)才能构成完整的锁相环回路,在具备正常的芯片功能的前提下才能实现对其相位噪声、杂散噪声下的测试。

一般而言,压控振荡器均使用现成的器件,在挑选器件时注意性能指标的匹配就可以,只有环路滤波器才是需要计算和设计的。环路滤波器在整个电路中主要作为一个低通滤波器,它将芯片鉴相器输出的脉冲信号进行低通滤波,将高频分量滤除,最终得到一个相对平滑的直流电压信号去控制VCO工作,从而获得一个稳定的频率输出。环路滤波器的性能将直接影响到小数分频频率合成器芯片性能的测试。

本文以ADF 4153型小数分频频率合成器为例,给出了容易实现的三阶环路滤波器的设计方法,能够满足芯片实际测试的需要。

外接环路滤波器的设计

环路滤波器是电荷泵锁相环电路的重要环节,它连接在电荷泵和压控振荡器之间。锁相环的基本频率特性是由环路滤波器决定的。实际上,正是由于环路滤波器的存在,锁相环才可以选择工作在任意的中心频率和带宽内。环路滤波器的类型多种多样,大致分为有源滤波器和无源滤波器两大类,无源滤波器与有源滤波器相比,其优点在于:结构简单、低噪声、高稳定度和易以实现。

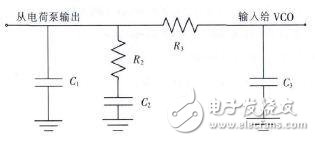

最常见的无源滤波器是如图1所示的三阶滤波器。一般而言,环路滤波器的带宽应为PFD频率(通道间隔)的1/10.提高环路带宽会缩短锁定时间。但环路带宽过大会大幅度地增加不稳定性,从而导致锁相环无法锁定的状态。

图1三阶环路滤波器

环路滤波器设计参数的选择

为了研究环路滤波器对锁相环输出频率相位噪声的影响,设计出符合芯片测试需要的外围环路滤波器。我们在ADIsimPLL软件中进行了如下仿真配置。器件型号:ADF 4153,fPFD=25MHz(理想信号源),INT=69,FRAC=101,MOD=125,VCO采用ZComm公司的V674ME34-LF,在该配置下,预期输出的RFOUT=1.7452GHz.

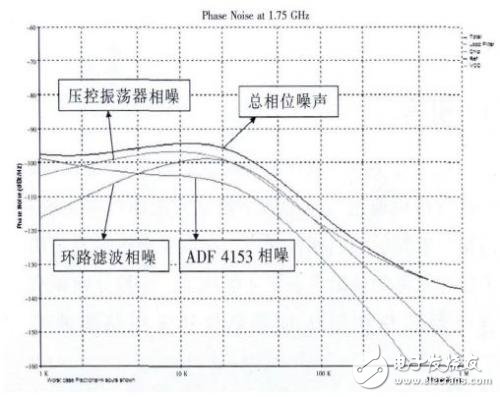

a)设定环路滤波器带宽为20kHz,相位裕度50°,其相位噪声的仿真情况如图2所示。

图2环路带宽20kHz时的相位噪声仿真图

从图2中可以得知,当环路滤波带宽为20kHz时,VCO所引起的相位噪声占据了主导地位。芯片所引起的相位噪声则被淹没在总输出噪声之下。换句话说,当环路带宽较窄(如20kH)的情况下,针对锁相环输出信号进行相位噪声测试,其结果并不能真正地反映芯片输出的相位噪声。

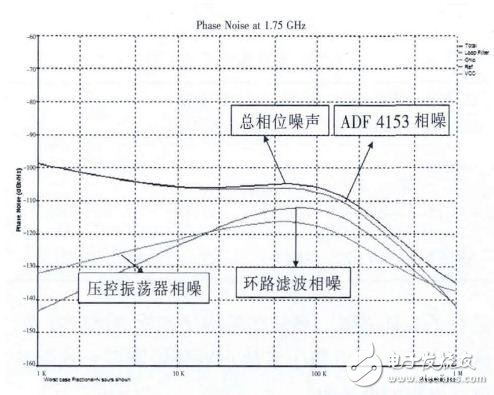

设定环路滤波器带宽为100kHz,相位裕度50°,其相位噪声的仿真情况如图3所示。

图3环路带宽为100kHz时的相位噪声仿真图

从图3中可以得知,当环路滤波带宽为100kHz时,VCO对于总相位噪声的贡献显著地降低,芯片所引起的相位噪声占据了主导地位,在10kHz以内,总相位噪声输出的曲线基本与芯片所引起的相位噪声重合。由此可以得知,当环路带宽较宽(如 100kHz)的情况下,针对锁相环输出信号进行相位噪声测试,其结果基本能真正反映芯片输出的相位噪声。

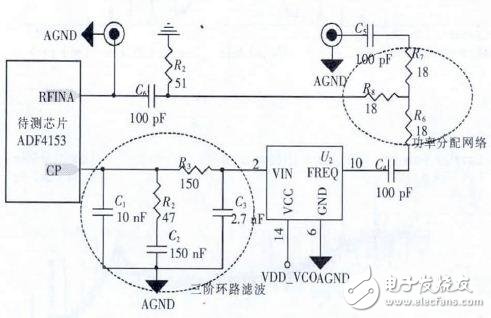

本文研究的ADF 4154的主要测试频点为1.7452GHz(fPFD=25MHz,RSET=5.1k),根据测试要求进行综合的考虑,设定了环路带宽75kHz,相位裕度50°的约束条件。在进行ADF 4153的外围电路设计时,首先需要确认所使用的VCO型号及其标称性能。然后再根据ADI公司提供的ADIsim-PLL软件进行三阶环路滤波器的设计。从软件得出C1~C3、R2、R3的具体取值,再根据现有的标称电容电阻值进行调整,反算出实际设计的环路带宽及相位裕度。

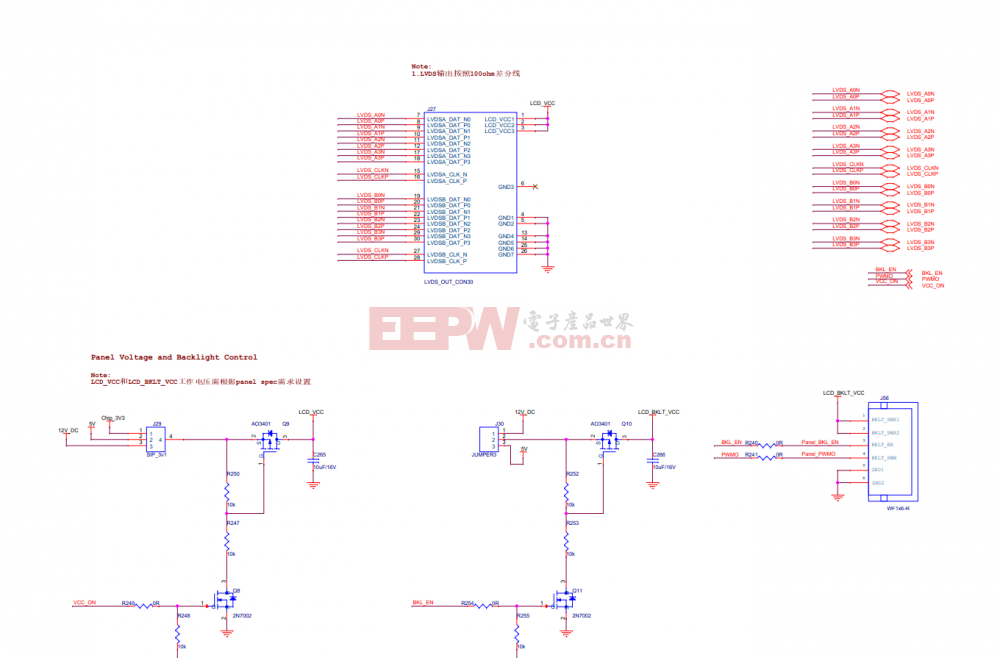

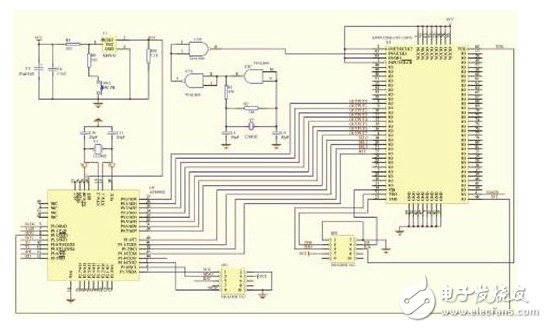

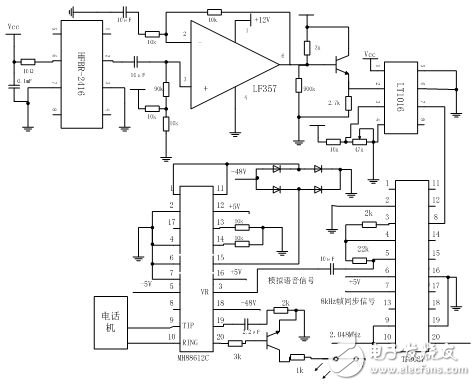

由此,我们确定了环路滤波器中各个电容、电阻的取值,并设计了可用于ADF 4153芯片测试的电路原理图,如图4所示。VCO的输出不仅需要连接外部频谱仪进行测试,还需要通过电容反馈到ADF 4153的REFINA端,同时REFINA端还需要预留SMA头用于射频输入频率范围及灵敏度测试。一个简单的电阻网络用于完成VCO输出信号功率的再分配。

图4环路滤波器及射频电路设计

本文主要基于芯片测试目的,针对外围电路中的环路滤波器设计来进行讨论,文中给出了一种简单、易行的工程化计算方法和流程,并对其进行了验证测试,测试结果满足芯片测试的需要。这种方法已经应用于多款小数分频频率合成器的测试电路的设计中。

Tags:

相关文章

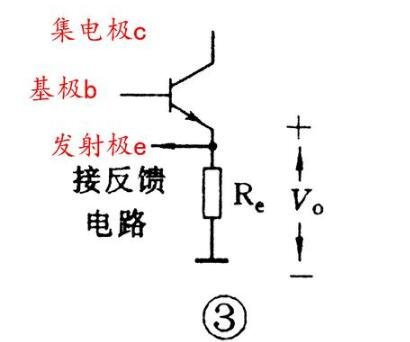

- 串联和并联反馈放大电路图-信号处理电子电路图

- 基于ZigBee协议的无线通讯硬件电路设计图-信号处理电子电路图

- 信号机电路图讲解和实物图(黄灯点灯电路/出站信号机点灯/进站信号机点灯电路)-信号处理电子电路图

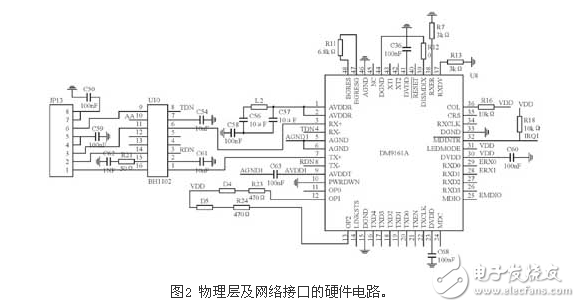

- 以太网收发电路设计方案详解-信号处理电子电路图

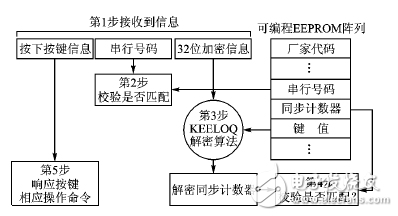

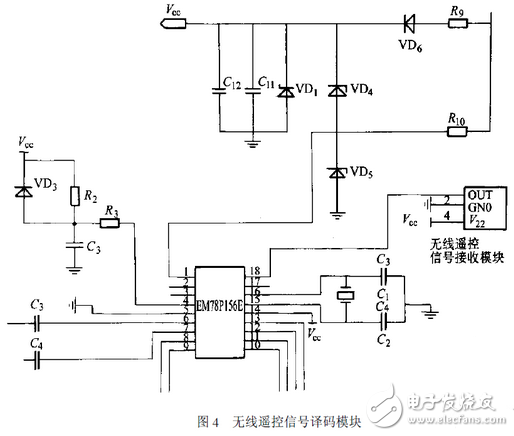

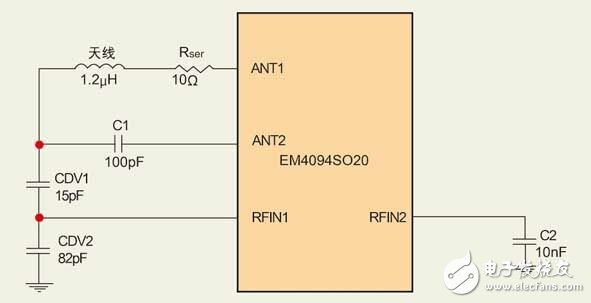

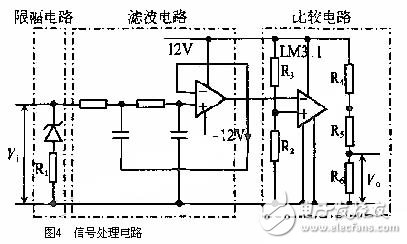

- 无线遥控信号处理电路设计详解-信号处理电子电路图

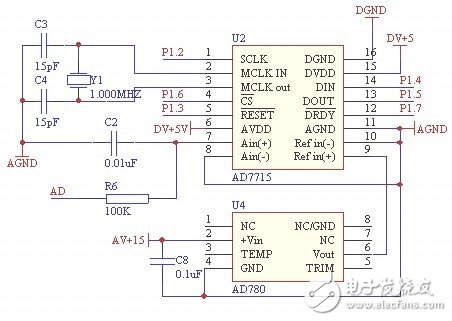

- 具有调零及满度功能的信号处理电子电路图-信号处理电子电路图

- 智能照明系统室内环境光采集电路图-信号处理电子电路图

- 智能电表中的RS485的通讯模块电路设计-信号处理电子电路图

- 解读多间隔脉冲信号连接器电路-信号处理电子电路图

- 采用ADAS3023同步数据采集系统电路 —电路图天天读(37)-信号处理电子电路图

猜你喜欢

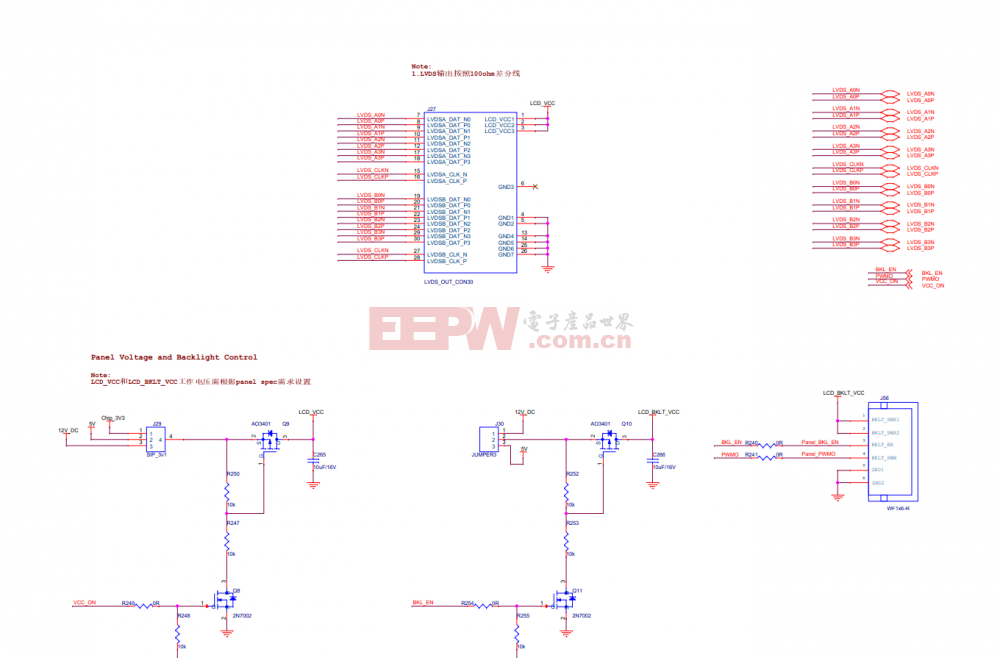

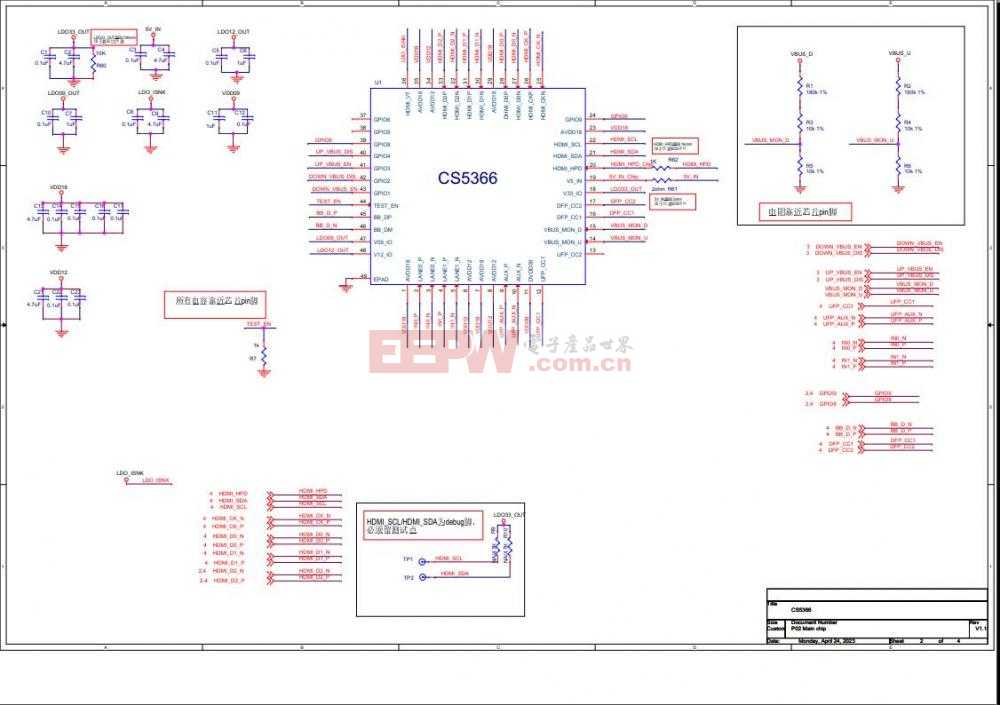

CS5511国产DP转LVDS/eDP方案设计电路图-信号处理电子电路图

CS5511是一款适用于低成本显示系统的灵活配置的DP/eDP到LVDS/eDP转换器。CS5511原理...

时钟有回沟?什么原因会导致信号波形边沿的回沟?-信号处理电子电路图

什么原因会导致信号波形边沿的回沟? 信号传输过程中遇到阻抗不连续会产生...

反相加法运算电路,反相积分运算电路(含分析和计算公式)-信号处理电子电路图

集成运算放大器是一种高增益的直流放大器。它有两个输入端,一个输出端。...

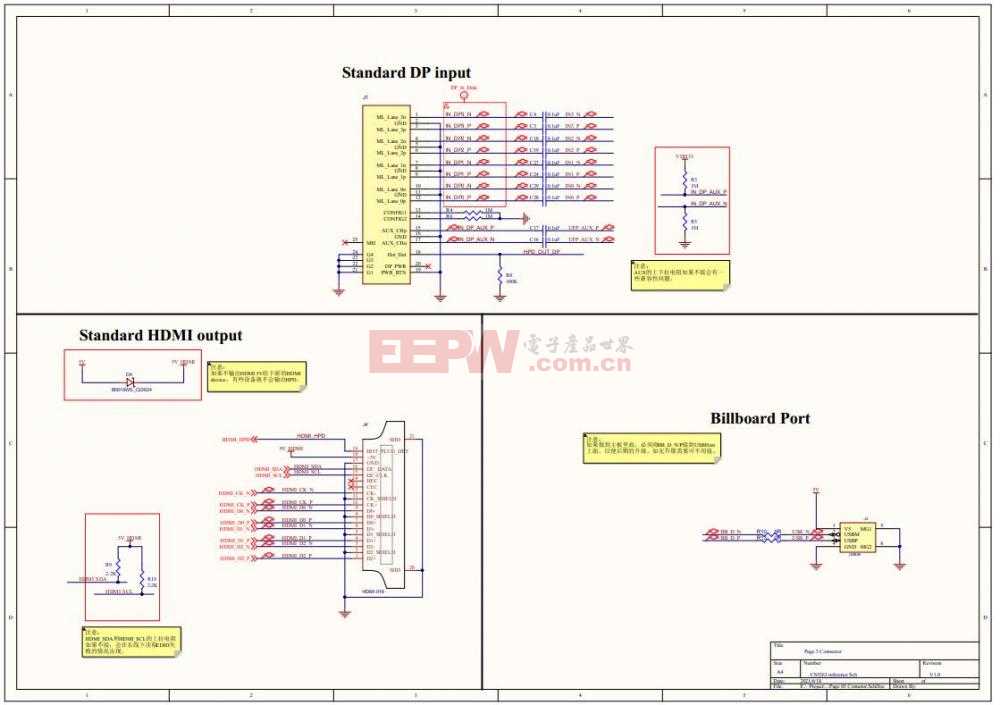

TYPEC转HDMI 8K30HZ+USB3.0+PD100W扩展方案CS5466芯片原理图-信号处理电子电路图

CS5466芯片原理图,CS5466单芯片集成Type-C转HDMI8K30HZ或者4K144HZ方案芯片, TYPEC转...

信号处理相关资讯

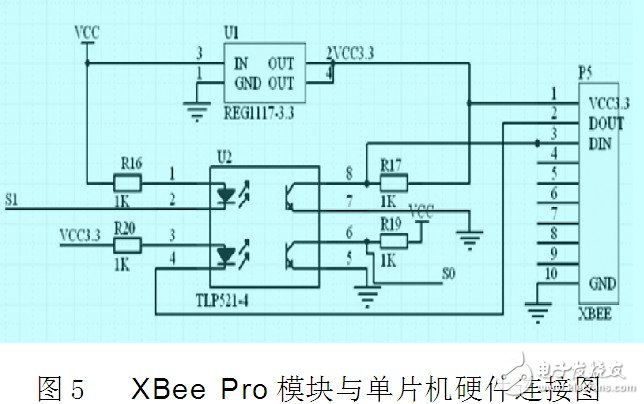

解读ZigBee无线终端温度测试系统电路 —电路图天天读(85)-信号处理电子电路图

CS5511国产DP转LVDS/eDP方案设计电路图-信号处理电子电路图

用D-CAP模式的TPS53355芯片如何设计RCC纹波电路-信号处理电子电路图

CS5263电路原理图|替代IT6561芯片电路|DP转HDMI芯片方案设计-信号处理电子电路图

射频无线门禁系统电路设计方案详解 —电路图天天读(114)-信号处理电子电路图

微压力传感连接器电路设计详解-信号处理电子电路图

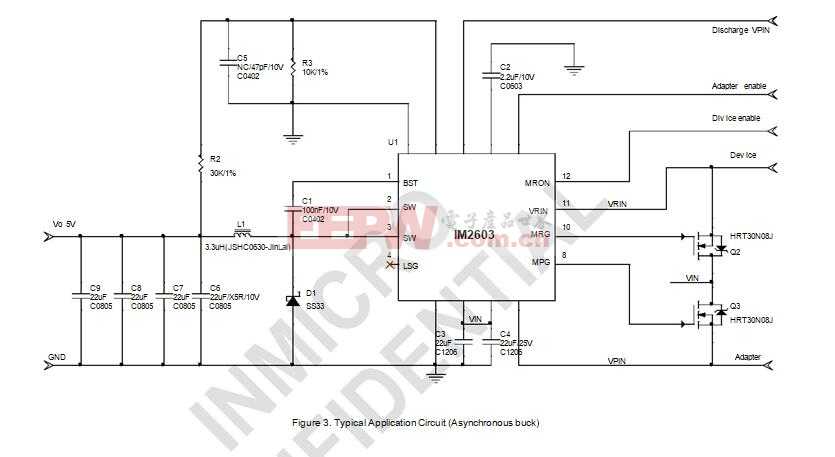

IM2603替代MT3905升降压MOS电源芯片-信号处理电子电路图

采用QCM传感器的差频与控制电路设计-信号处理电子电路图

电压和电流反馈放大电路图-信号处理电子电路图

无线智能照明控制系统电路详解-信号处理电子电路图

基于NFC通用读卡器电路设计 —电路图天天读(42)-信号处理电子电路图

汽车传感器之信号处理电路设计-信号处理电子电路图

基于CO2128的网络信号转换系统电路设计-信号处理电子电路图

一种电话语音信号光纤接收机电路设计-信号处理电子电路图

ASL CS5466设计TYPEC转HDMI 8K高清扩展投屏方案芯片电路-信号处理电子电路图