您现在的位置是:主页 > 基础 > 数字电路图 >

74ls138和74ls20设计的三人表决器-数字电路图

发布时间:2023-02-25 12:26:32所属栏目:数字电路图 已帮助人编辑作者:电路图知识网

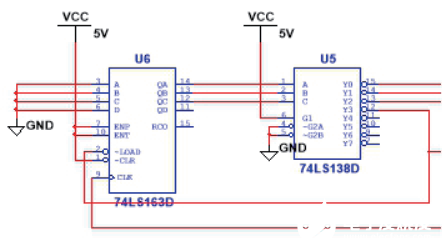

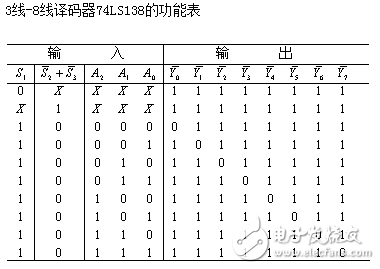

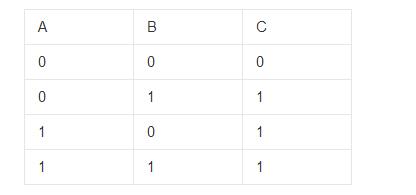

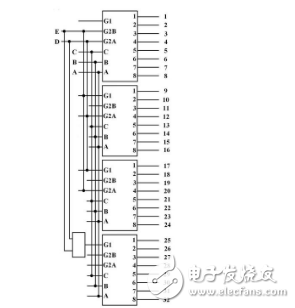

74ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。

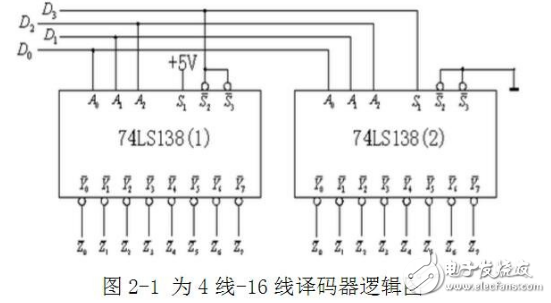

①当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

②利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

③若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

④可用在8086的译码电路中,扩展内存。

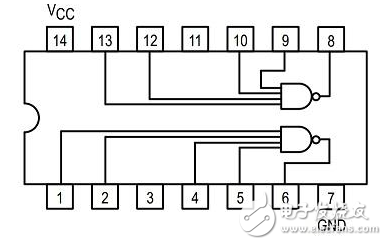

74ls20是一个四输入一输出的与非门组合的芯片,逻辑功能是完成四个输入的逻辑与非计算功能,1、2、4、5脚输入,6脚输出,13、12、10、9脚输入,8脚输出,3、11两个脚空的,7脚接GND,14脚接Vcc。

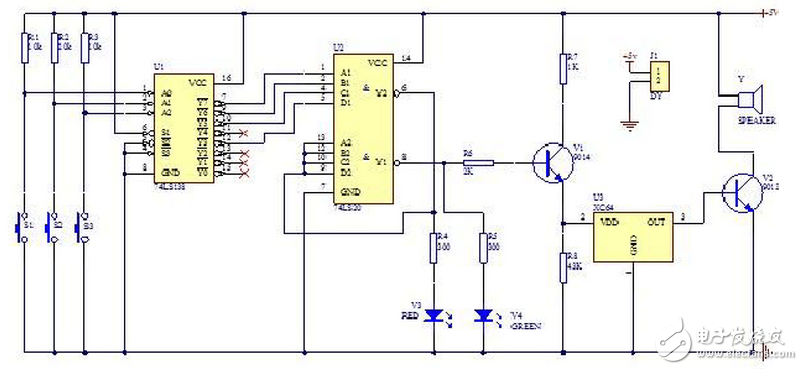

三人表决器主要由一个3-8位译码器(74LS138)和2个4输入与非门(74LS20)组成。通过三个按钮接受用户输入。按钮按下表示同意,不按下表是否决,当没有人按下按钮时,或只有一个人按下按钮时,例如,S1按下,而S2和S0未按下,则红灯亮,绿灯灭,蜂鸣器无声音,表示否决,当有两个人及以上的人按下按钮后,例如,S1和S2按下,则红灯灭,绿灯亮,蜂鸣器发音,表示通过。运用74LS138译码器和四输入与非门74LS20实现该逻辑功能。

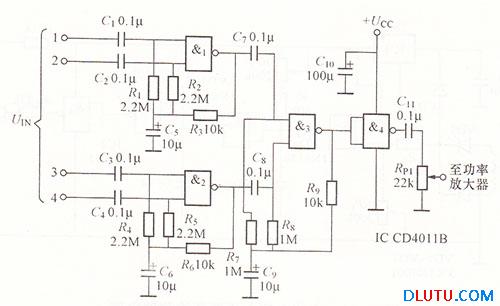

74ls138和74ls20设计的三人表决器电路图

Tags:

相关文章

数字电路图相关资讯

设计抗混叠滤波器的三大指导原则-数字电路图

采用C-MOS IC 的计数分频器电路-数字电路图

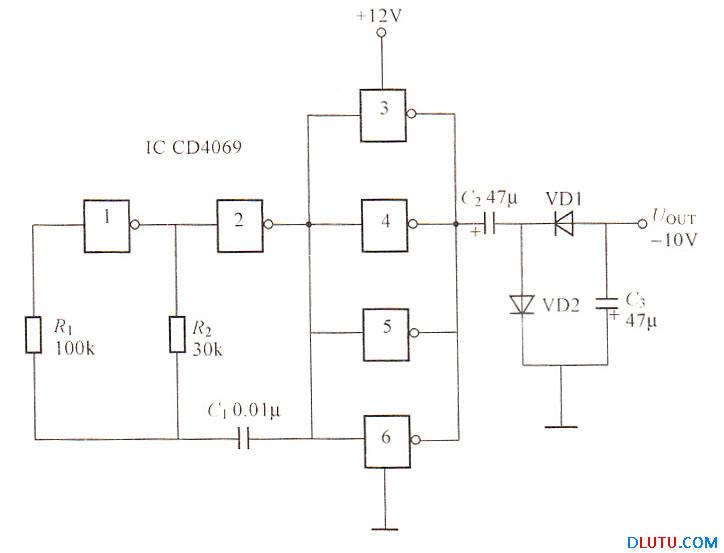

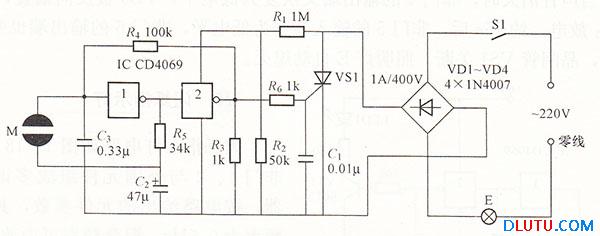

由CD4069构成的负压变换器电路图-数字电路图

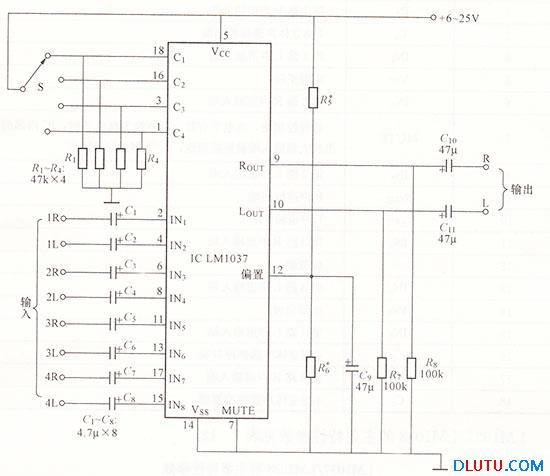

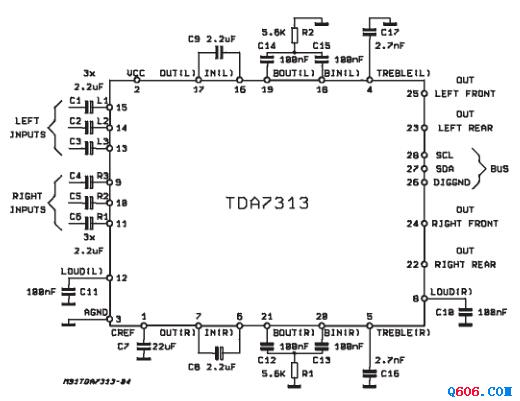

LM1037的基本应用电路图-数字电路图

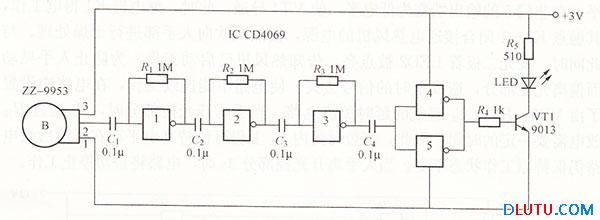

简易心率测试仪电路图-数字电路图

四声道输出数字控制音频处理芯片-数字电路图

照明灯触摸开关电路图-数字电路图

门电路作用是什么_门电路有几种电路-数字电路图

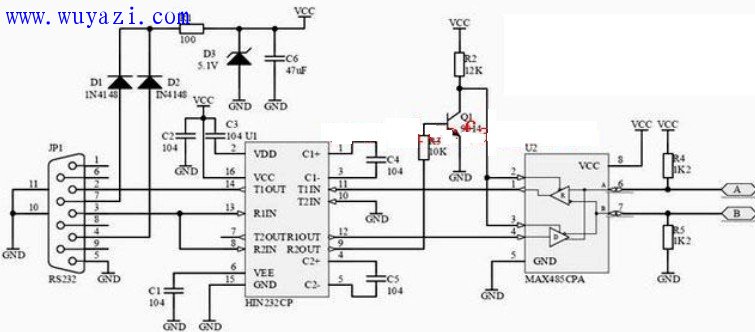

自制RS232-485转换器电路图-数字电路图

家用节电灯的电路图-数字电路图

DC-RRS应用电路b-数字电路图

74HC138组成32线译码器的电路图 74HC138组成32线译码器方法-数字电路图

解析数字电路抗干扰问题-数字电路图

LC振荡器的比较-变压器反馈式振荡器-数字电路图

四路混声器电路图-数字电路图